定时任务理解

定时任务理解

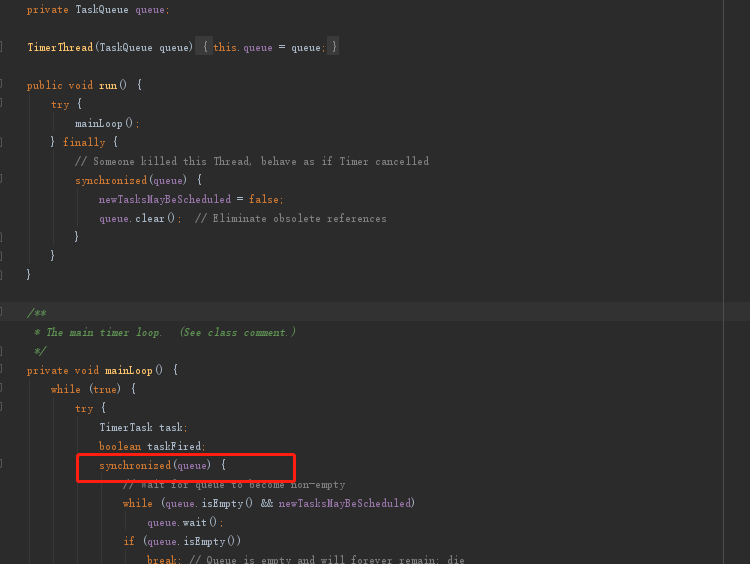

在工具类Timer中,提供了四个构造方法,每个构造方法都启动了计时器线程,同时Timer类可以保证多个线程可以共享单个Timer对象而无需进行外部同步,所以Timer类是线程安全的。由此可见,Timer里面的定时任务线程组是用queue队列执行,并且主线程执行定时任务队列用了synchronized同步机制,所以定时任务必须串联执行,Timer在执行定时任务时只会创建一个线程任务,如果存在多个线程任务,多个任务之间的时间间隔一定要大于任务本身的执行时间,不然后面的任务就会延迟。相对来说quartz实现就规避了Timer的问题,不仅多任务之间不会相互影响,单任务循环任务之间也不会相互影响。

Timer实现如下截图

由定时任务引发的思考:触发器

用函数结构来理解,针对前触发和后触发其实只是在调用函数前执行和调用函数后执行,有点像面向切面插入。

触发器的电路结构与工作原理

触发器的记忆功能

时序逻辑电路

触发器:触发器是构成时序逻辑电路的基本逻辑单元,能够存储一位二值信息的基本单元电路。

基本特点

1、具有两个能够自行保存的稳定状态,用来表示逻辑状态0和1。

2、根据不同的输入信号,可以输出置成0或1。

3、输入信号消失后,能将获取的状态保存下来。

分类

电路结构:基本RS触发器/同步RS触发器/主从触发器/边沿触发器/时钟触发器

逻辑特性:RS触发器(置0,置1,保持,不定)/JK触发器(置0,置1,保持,计数)/D触发器(置0,置1)/T触发器(保持,计数)

“时钟是时序电路的控制者” 这句话太经典了,可以说是FPGA设计的圣言。FPGA的设计主要是以时序电路为主,因为组合逻辑电路再怎么复杂也变不出太多花样,理解起来也不没太多困难。但是时序电路就不同了,它的所有动作都是在时钟一拍一拍的节奏下转变触发,可以说时钟就是整个电路的控制者,控制不好,电路功能就会混乱。

打个比方,时钟就相当于人体的心脏,它每一次的跳动就是触发一个 CLK,向身体的各个器官供血,维持着机体的正常运作,每一个器官体统正常工作少不了组织细胞的构成,那么触发器就可以比作基本单元组织细胞。时序逻辑电路的时钟是控制时序逻辑电路状态转换的“发动机”,没有它时序逻辑电路就不能正常工作,因为时序逻辑电路主要是利用触发器存储电路的状态,而触发器状态变换需要时钟的上升或下降沿!由此可见时钟在时序电路中的核心作用!

晶振两脚产生的14.318MHz基本频率输入到时钟芯片内部的振荡器,从振荡器出来的基本频率经过“频率扩展锁相网路”进行频率扩展后输入到各个分频器,最后得到不同频率的时钟输出。

电脑主板的各个部分就是通过时钟信号输入还获取时钟脉冲。

个人理解,不喜勿喷。